Evaluation Platforms: Difference between revisions

(Add LX200 description) |

(ISS is really another evaluation platform, so move it here, and adjust intro text a bit) |

||

| Line 2: | Line 2: | ||

= Evaluation and Prototyping Platforms = | = Evaluation and Prototyping Platforms = | ||

The following boards and | The following boards and simulators can be used for evaluation and prototyping purposes. Evaluation platforms generally fall into one of the following categories: | ||

* instruction set simulators, | |||

* emulation systems that use FPGAs to implement any Xtensa or Diamond core (within the capacity of the FPGAs), and | |||

* boards that integrate a specific configured Xtensa or Diamond core(s) into an ASIC. | |||

Field programmable gate arrays (FPGA) contain programmable logic that can be re-configured to emulate complex logic. Although slower than the dedicated circuitry of an ASIC (application specific integrated circuit), their re-configurability and practically zero NRE make them very useful for prototyping (for example, trying multiple Xtensa processor variants or configurations) or small volume applications. | |||

== Instruction Set Simulator == | |||

Instruction Set Simulators (ISS) mimic the behavior of processors by simulating instructions, memory interface, and other I/O components. This allows developers to run and test their software long before real hardware becomes available. Functional simulators provide the best performance, whereas cycle-accurate simulators provide timing accuracy compatible to that of real hardware. The latter simulate the processor pipeline and external components synchronized to a virtual clock. Although this overhead reduces their performance, it can provide vital information to improve the implementation of algorithms. | |||

=== Tensilica ISS === | |||

[http://www.tensilica.com/ Tensilica] offers a commercial functional simulator (TurboXim) and cycle-accurate simulator for the Xtensa processor architecture, as part of their standard software development tools. (You may be able to try a free limited time evaluation copy of this toolset.) Tensilica also offers XTMP and XTSC for modeling systems of one or multiple processors alongside custom functional or cycle-accurate software models for other components. Please visit [http://www.tensilica.com/ Tensilica's] website for further information. | |||

The standalone simulator (xt-iss), for example, simply takes an ELF file as its argument and starts simulating instructions from the reset vector. The option <code>--turbo</code> invokes the (much faster) functional simulator TurboXim. | |||

xt-iss ''[--turbo]'' Image.elf | |||

== Emulation Platforms and Systems == | == Emulation Platforms and Systems == | ||

| Line 12: | Line 28: | ||

with a 10/100 Ethernet PHY, DDR memory, flash memory, serial port, and 2 x 16 character LCD panel. The MAC controller, however, needs to be implemented inside the FPGA. MAC controllers are available from different vendors. [http://opencores.org OpenCores], for example, provides a free Ethernet controller supported by Linux and other operating systems. The [http://www.em.avnet.com/tensilica2 LX200] is based on the Xilinx XC4VLX200 and can emulate more complex processor configurations and extensions (for example the [http://www.tensilica.com/products/hifi_audio.htm HiFi 2 Audio Engine]) and provides the same components as the LX60 except for the LCD panel. | with a 10/100 Ethernet PHY, DDR memory, flash memory, serial port, and 2 x 16 character LCD panel. The MAC controller, however, needs to be implemented inside the FPGA. MAC controllers are available from different vendors. [http://opencores.org OpenCores], for example, provides a free Ethernet controller supported by Linux and other operating systems. The [http://www.em.avnet.com/tensilica2 LX200] is based on the Xilinx XC4VLX200 and can emulate more complex processor configurations and extensions (for example the [http://www.tensilica.com/products/hifi_audio.htm HiFi 2 Audio Engine]) and provides the same components as the LX60 except for the LCD panel. | ||

[http://www.tensilica.com Tensilica] provides a bitstream that describes the configuration data to emulate the DC232L | [http://www.tensilica.com Tensilica] provides a bitstream that describes the configuration data to emulate the Diamond Standard DC232L processor (Rev.B) on the LX60 FPGA. Tensilica refers to this board and bitstream combination as the XTAV60 board. It also includes support for the OpenCores Ethernet MAC. For further information, please, contact [http://www.tensilica.com/company/contact_us.htm Tensilica] directly. | ||

=== Eve ZeBu === | === Eve ZeBu === | ||

| Line 20: | Line 36: | ||

See the [[Linux on ZeBu]] page or contact [http://www.eve-team.com Eve] directly to request additional information. | See the [[Linux on ZeBu]] page or contact [http://www.eve-team.com Eve] directly to request additional information. | ||

== | == ASIC Evaluation Platforms == | ||

=== Stretch S55DVKxx and S56DVKxx === | === Stretch S55DVKxx and S56DVKxx === | ||

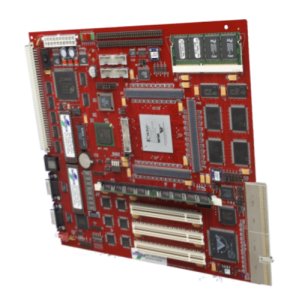

[http://www.stretchinc.com Stretch] provides software-configurable processors based on the Xtensa architecture. The S5000 processor supports Linux, and at 300MHz, it runs 5-10 times faster than emulation platforms. The S55DVKxx and S56DVKxx development platforms provide 10/100/1000 Ethernet, serial, PCI (only S56DVKxx), and other interfaces. | [http://www.stretchinc.com Stretch] provides software-configurable processors based on the Xtensa architecture. The S5000 processor supports Linux, and at 300MHz, it runs 5-10 times faster than FPGA based emulation platforms. The S55DVKxx and S56DVKxx development platforms provide 10/100/1000 Ethernet, serial, PCI (only S56DVKxx), and other interfaces. | ||

The Stretch platforms come with RedBoot as the bootloader. It can download and boot the kernel over network using TFTP or from flash. Make sure that RedBoot is configured with a valid Ethernet address or set to DHCP to obtain a valid address. The following commands load the kernel image ''zImage.redboot'' and boot the kernel: | The Stretch platforms come with RedBoot as the bootloader. It can download and boot the kernel over network using TFTP or from flash. Make sure that RedBoot is configured with a valid Ethernet address or set to DHCP to obtain a valid address. The following commands load the kernel image ''zImage.redboot'' and boot the kernel: | ||

Revision as of 21:13, 9 December 2008

Evaluation and Prototyping Platforms

The following boards and simulators can be used for evaluation and prototyping purposes. Evaluation platforms generally fall into one of the following categories:

- instruction set simulators,

- emulation systems that use FPGAs to implement any Xtensa or Diamond core (within the capacity of the FPGAs), and

- boards that integrate a specific configured Xtensa or Diamond core(s) into an ASIC.

Field programmable gate arrays (FPGA) contain programmable logic that can be re-configured to emulate complex logic. Although slower than the dedicated circuitry of an ASIC (application specific integrated circuit), their re-configurability and practically zero NRE make them very useful for prototyping (for example, trying multiple Xtensa processor variants or configurations) or small volume applications.

Instruction Set Simulator

Instruction Set Simulators (ISS) mimic the behavior of processors by simulating instructions, memory interface, and other I/O components. This allows developers to run and test their software long before real hardware becomes available. Functional simulators provide the best performance, whereas cycle-accurate simulators provide timing accuracy compatible to that of real hardware. The latter simulate the processor pipeline and external components synchronized to a virtual clock. Although this overhead reduces their performance, it can provide vital information to improve the implementation of algorithms.

Tensilica ISS

Tensilica offers a commercial functional simulator (TurboXim) and cycle-accurate simulator for the Xtensa processor architecture, as part of their standard software development tools. (You may be able to try a free limited time evaluation copy of this toolset.) Tensilica also offers XTMP and XTSC for modeling systems of one or multiple processors alongside custom functional or cycle-accurate software models for other components. Please visit Tensilica's website for further information.

The standalone simulator (xt-iss), for example, simply takes an ELF file as its argument and starts simulating instructions from the reset vector. The option --turbo invokes the (much faster) functional simulator TurboXim.

xt-iss [--turbo] Image.elf

Emulation Platforms and Systems

Avnet Virtex-4 LX60 and LX200

Avnet offers the following development platforms for the Xilinx Virtex-4 LX FPGA that can emulate various Xtensa processor configurations. The LX60 is based on the Xilinx 4VLX60 and comes with a 10/100 Ethernet PHY, DDR memory, flash memory, serial port, and 2 x 16 character LCD panel. The MAC controller, however, needs to be implemented inside the FPGA. MAC controllers are available from different vendors. OpenCores, for example, provides a free Ethernet controller supported by Linux and other operating systems. The LX200 is based on the Xilinx XC4VLX200 and can emulate more complex processor configurations and extensions (for example the HiFi 2 Audio Engine) and provides the same components as the LX60 except for the LCD panel.

Tensilica provides a bitstream that describes the configuration data to emulate the Diamond Standard DC232L processor (Rev.B) on the LX60 FPGA. Tensilica refers to this board and bitstream combination as the XTAV60 board. It also includes support for the OpenCores Ethernet MAC. For further information, please, contact Tensilica directly.

Eve ZeBu

Eve offers an emulation and verification system that can be used to emulate Xtensa processors. Similar to FPGA boards, the ZeBu system emulates the processor, but has a higher capacity to emulate larger processor configurations and additional peripherals. It also provides direct access to signals for debugging and verification.

See the Linux on ZeBu page or contact Eve directly to request additional information.

ASIC Evaluation Platforms

Stretch S55DVKxx and S56DVKxx

Stretch provides software-configurable processors based on the Xtensa architecture. The S5000 processor supports Linux, and at 300MHz, it runs 5-10 times faster than FPGA based emulation platforms. The S55DVKxx and S56DVKxx development platforms provide 10/100/1000 Ethernet, serial, PCI (only S56DVKxx), and other interfaces.

The Stretch platforms come with RedBoot as the bootloader. It can download and boot the kernel over network using TFTP or from flash. Make sure that RedBoot is configured with a valid Ethernet address or set to DHCP to obtain a valid address. The following commands load the kernel image zImage.redboot and boot the kernel:

RedBoot> load -r -b 0xd0200000 -h 192.168.1.5 zImage.redboot RedBoot> exec 0xd0200000

Note that RedBoot requires that the tftp host is in the same subnet as the board.